- 您现在的位置:买卖IC网 > Sheet目录473 > MAX2769EVKIT+ (Maxim Integrated)KIT EVAL FOR MAX2769

�� �

�

�

�MAX2769�

�Universal� GPS� Receiver�

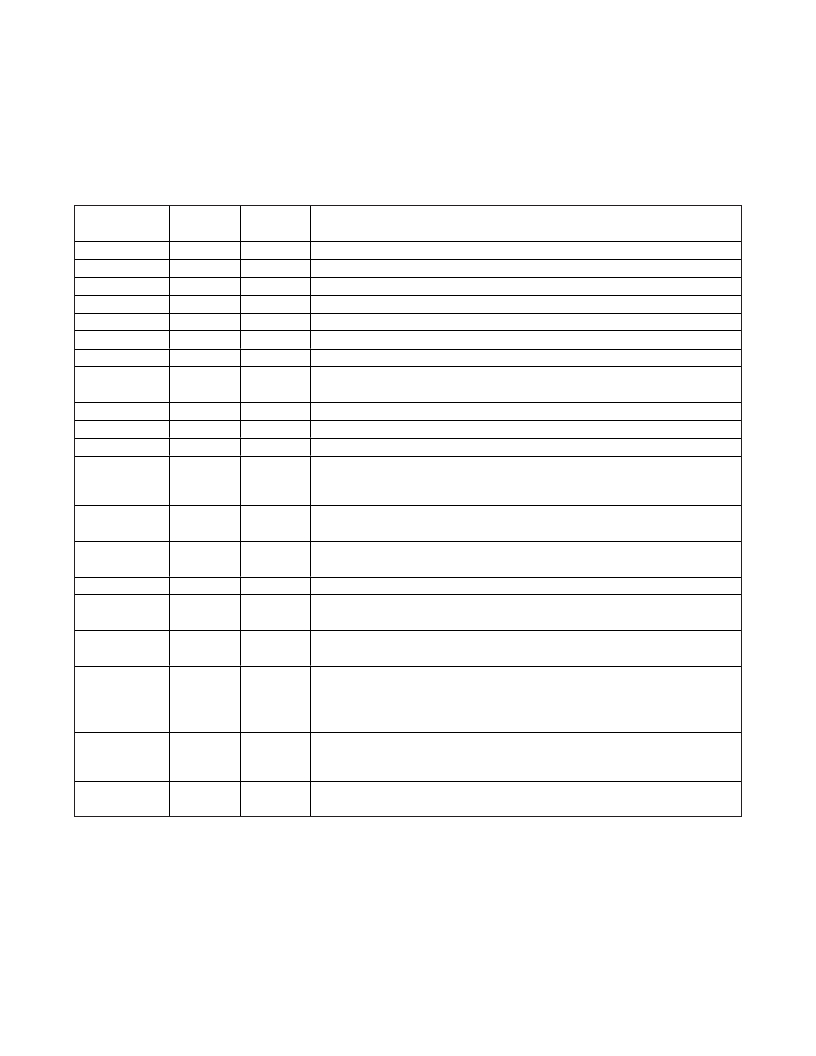

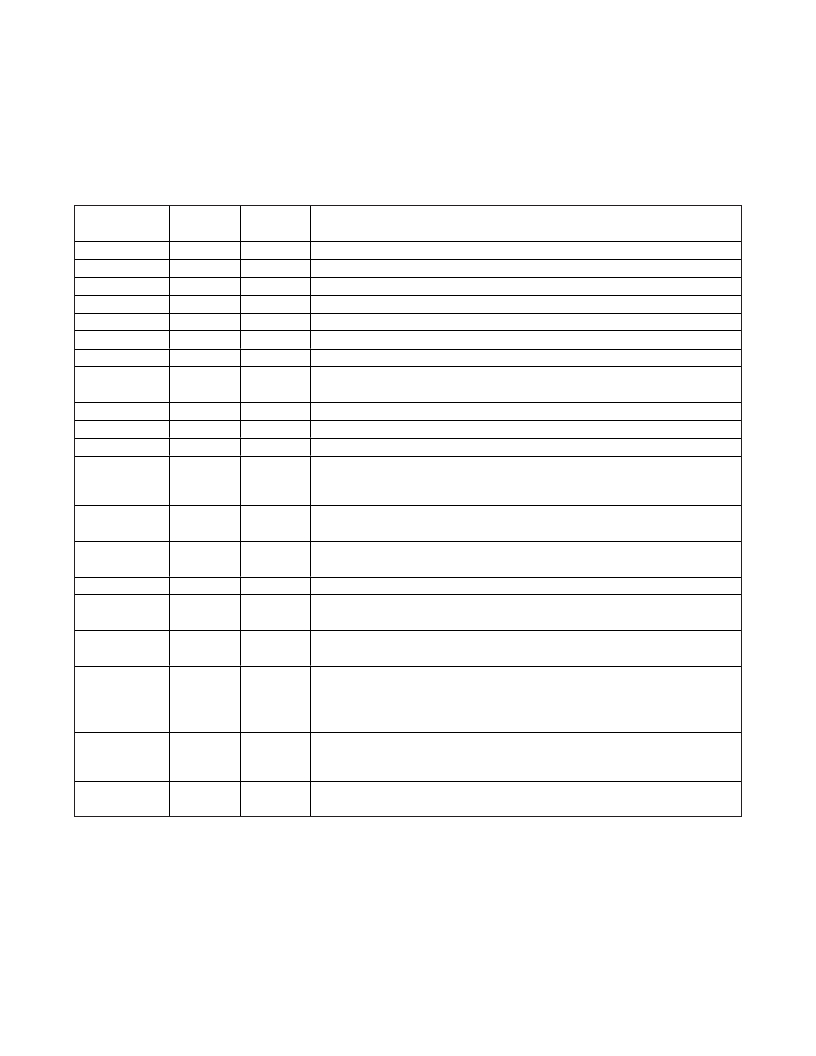

�Table� 8.� Configuration� 3� (Address:� 0010)�

�DATA� BIT�

�GAININ�

�FSLOWEN�

�HILOADEN�

�ADCEN�

�DRVEN�

�FOFSTEN�

�FILTEN�

�FHIPEN�

�—�

�PGAIEN�

�PGAQEN�

�LOCATION�

�27:22�

�21�

�20�

�19�

�18�

�17�

�16�

�15�

�14�

�13�

�12�

�DEFAULT�

�VALUE�

�111010�

�1�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�DESCRIPTION�

�PGA� gain� value� programming� from� the� serial� interface� in� steps� of� dB� per� LSB.�

�Low� value� of� the� ADC� full-scale� enable.� Set� 1� to� enable� or� 0� to� disable.�

�Set� 1� to� enable� the� output� driver� to� drive� high� loads.�

�ADC� enable.� Set� 1� to� enable� ADC� or� 0� to� disable.�

�Output� driver� enable.� Set� 1� to� enable� the� driver� or� 0� to� disable.�

�Filter� DC� offset� cancellation� circuitry� enable.� Set� 1� to� enable� the� circuitry� or� 0� to�

�IF� filter� enable.� Set� 1� to� enable� the� filter� or� 0� to� disable.�

�Highpass� coupling� enable.� Set� 1� to� enable� the� highpass� coupling� between� the� filter�

�and� PGA,� or� 0� to� disable� the� coupling.�

�Reserved.�

�I-channel� PGA� enable.� Set� 1� to� enable� PGA� in� the� I� channel� or� 0� to� disable.�

�Q-channel� PGA� enable.� Set� 1� to� enable� PGA� in� the� Q� channel� or� 0� to� disable.�

�DSP� interface� for� serial� streaming� of� data� enable.� This� bit� configures� the� IC� such�

�STRMEN�

�11�

�0�

�that� the� DSP� interface� is� inserted� in� the� signal� path.� Set� 1� to� enable� the� interface�

�or� 0� to� disable� the� interface.�

�STRMSTART�

�STRMSTOP�

�STRMCOUNT�

�STRMBITS�

�STAMPEN�

�10�

�9�

�8:6�

�5:4�

�3�

�0�

�0�

�111�

�01�

�1�

�The� positive� edge� of� this� command� enables� data� streaming� to� the� output.� It� also�

�enables� clock,� data� sync,� and� frame� sync� outputs.�

�The� positive� edge� of� this� command� disables� data� streaming� to� the� output.� It� also�

�disables� clock,� data� sync,� and� frame� sync� outputs.�

�Sets� the� length� of� the� data� counter� from� 128� (000)� to� 16,394� (111)� bits� per� frame.�

�Number� of� bits� streamed.� D5:D4� =� 00:� I� MSB;� 01:� I� MSB,� I� LSB;� 10:� I� MSB,� Q� MSB;�

�11:� I� MSB,� I� LSB,� Q� MSB,� Q� LSB.�

�The� signal� enables� the� insertion� of� the� frame� number� at� the� beginning� of� each�

�frame.� If� disabled,� only� the� ADC� data� is� streamed� to� the� output.�

�This� signal� enables� the� output� of� the� time� sync� pulses� at� all� times� when� streaming�

�TIMESYNCEN�

�2�

�1�

�is� enabled� by� the� STRMEN� command.� Otherwise,� the� time� sync� pulses� are�

�available� only� when� data� streaming� is� active� at� the� output,� for� example,� in� the� time�

�intervals� bound� by� the� STRMSTART� and� STRMSTOP� commands.�

�This� control� signal� enables� the� sync� pulses� at� the� DATASYNC� output.� Each� pulse�

�DATSYNCEN�

�1�

�0�

�is� coincident� with� the� beginning� of� the� 16-bit� data� word� that� corresponds� to� a�

�given� output� bit.�

�STRMRST�

�Maxim� Integrated�

�0�

�0�

�This� command� resets� all� the� counters� irrespective� of� the� timing� within� the�

�stream� cycle.�

�19�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX2821ETM+T

IC TXRX 802.11B 2.4GHZ 48-TQFN

MAX2829EVKIT

EVAL KIT MAX2828, MAX2829

MAX2830EVKIT+

KIT EVAL FOR MAX2830

MAX2831EVKIT+

KIT EVAL FOR MAX2831

MAX2837EVKIT+

KIT EVAL FOR MAX2837

MAX2838EVKIT+

KIT EVAL FOR MAX2838

MAX2839ASEVKIT+

KIT EVAL FOR MAX2839A WLP

MAX2839EVKIT+

KIT EVAL FOR MAX2839

相关代理商/技术参数

MAX-277

制造商:MDE 制造商全称:MDE Semiconductor, Inc. 功能描述:HIGH CURRENT TRANSIENT VOLTAGE SUPPRESSOR

MAX280C/D

功能描述:有源滤波器 RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube

MAX280CPA

功能描述:有源滤波器 RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube

MAX280CPA+

功能描述:有源滤波器 5th-Order Zero-Error Butterworth RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube

MAX280CWE

功能描述:有源滤波器 Integrated Circuits (ICs) RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube

MAX280CWE+

功能描述:有源滤波器 5th-Order Zero-Error Butterworth RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube

MAX280CWE+T

功能描述:有源滤波器 5th-Order Zero-Error Butterworth RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube

MAX280CWE-T

功能描述:有源滤波器 RoHS:否 制造商:Maxim Integrated 通道数量:1 截止频率:150 KHz 电源电压-最大:11 V 电源电压-最小:4.74 V 最大工作温度:+ 85 C 安装风格:Through Hole 封装 / 箱体:PDIP N 封装:Tube